Smartcard-type FPGA board for PUF and EMA experimentation

MiMICC is a new FPGA board that has close dimension to ID-1 format of ISO/IEC 7810 standards. MiMICC is developed for experimentation of Physical Unclonable Function (PUF) and Electromagnetic Analyais (EMA). MiMICC was developed in the CREST (Core Research for Evolutional Science and Technology) project funded by JST (Japan Science and Technology Agency).

MiMICC requires much larger power supply than general smartcards during FPGA configuration. Many of the general smartcard readers seem not to have enough power to drive MiMICC. Users are recommended to use SASEBO-W which is able to drive MiMICC. Note that MiMICC is just an FPGA board; MiMICC does not work as a smartcard unless you implement an emulator circuit of a smartcard on it.

|

MiMICC (Miniture Measurement IC Card) |

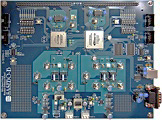

SCA experimental platform for education use

We move on to next step of research on SCA and FA methods. Thus, we plan to focus on evaluation algorithm and software. On the other hand, there is not facile board such as SASEBO-G. Measurement of a SASEBO-GIII requires advanced measurement skills, but the Virtex-II pro on G was discontinued, either. Because of the background, we develop a new simple board by employing Xilinx previous-generation device, Spartan-3A. AIST worked on CREST (Core Research for Evolutional Science and Technology) project funded by JST (Japan Science and Technology Agency).

|

ZUIHO, the First Educational Board with Xilinx Spartan-3A 1400/3400 DSP FPGA |

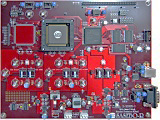

SASEBO-GIII/-RII

SASEBO-GIII, successor to the SASEBO-GII board, has newer FPGA devices. SASEBO-RII is a simplified board for cryptographic LSIs and employs SASEBO-W/ZUIHO as control hardware. AIST worked on CREST (Core Research for Evolutional Science and Technology) project funded by JST (Japan Science and Technology Agency).

|

SASEBO-GIII |

|

SASEBO-RII for cryptographic LSIs |

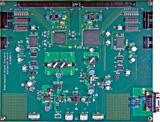

SASEBO-W

SASEBO-W was developed as testing environment for smartcards. Smartcard OS was also developed as an analysis target. AIST works on SPACES (Security evaluation of Physically Attacked Crypto processors in Embedded Systems) project funded by JST.

|

SASEBO-W for smartcards |

SASEBO-R/-G/-B/-GII (discontinued)

Side-channel Attack Standard Evaluation BOard (SASEBO) was developed as uniform evaluation environment of cryptographic modules. AIST and Tohoku University worked on this project funded by METI (Ministry of Economy, Trade and Industry, Japan).

|

SASEBO-R for cryptographic LSIs (discontinued) - Specification document - LSI control HW/SW (2012/04/02 version) |

|

SASEBO-G with Xilinx Virtex-II pro FPGA (discontinued) - Specification document - AES cryptographic circuit and control HW/SW (2012/04/02 version) |

|

SASEBO-B with Altera Stratix II FPGA (discontinued) - Specification document - AES cryptographic circuit and control HW/SW (2012/04/02 version) |

|

SASEBO-GII with Xilinx Virtex-5 FPGA

(discontinued) - Specification document - AES cryptographic circuit and control HW/SW (2012/04/02 version) |

|

Prototype SASEBO (discontinued) - Specification document |

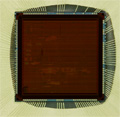

Cryptographic LSI

As analysis target, cryptographic LSIs were developed, which have ISO/IEC 18033-3 block ciphers and RSA. 130-nm and 90-nm TSMC version were fabricated in METI project. 65-nm e-shuttle version was fabricated in CREST project. The source codes of the ciphers are available on Tohoku University site.

|

130-nm TSMC - Specification document |

|

90/130-nm TSMC - Specification document |

|

65-nm e-shuttle - Specification document |

Contact

E-mail: sasebo_info-ml (at) aist.go.jp